BULLETIN OF THE POLISH ACADEMY OF SCIENCES TECHNICAL SCIENCES, Vol. 60, No. 4, 2012 DOI: 10.2478/v10175-012-0086-6

# Output characteristics of step-down (Buck) power converter

W. JANKE\*, M. BACZEK, and M. WALCZAK

Division of Electronic Systems, Technical University of Koszalin, 2 Śniadeckich St., 75-453 Koszalin, Poland

**Abstract.** The output characteristics of switched-mode dc-dc buck power converter are discussed. The shape of output characteristics is especially important for converters used for supplying modern processors. An output impedance is usually used for description of output characteristics. Many efforts are described in the literature to obtain the satisfastory features of closed-loop output impedance. Another approach, presented in the paper, is based on the concept of the output voltage response corresponding to the load conductance change, and is expressed by  $h_r$  transmittance. Simulations of output characteristics of the buck converter in frequency and in time-domain have been performed for the ideal case as well as for a more realistic situation, with the parasitic resistances of converter elements included. The measurement results differ substantially from characteristics calculated for an ideal converter and are in good consistency with simulations including parasitics.

Key words: DC-DC converters, output characteristics, load transients.

### 1. Introduction

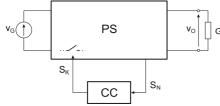

The group of DC-DC pulse-modulated converters is a broad class of power circuits with enormous range of applications. The typical power converter consists of the power stage (PS) and the control circuit (CC) as depicted in Fig. 1. The term "ideal converter" denotes a converter which power stage consists of ideal switches (zero voltage in ON state, zero current in *OFF* state) and the lossless linear inductors and capacitors. The switching frequency  $f_S$  is typically assumed to be constant and much higher than the power stage natural frequencies and the frequencies of eventual changes of input voltage and load conductance. The power converter, including the power stage and control circuit is a nonlinear, dynamical system with feedback, therefore the analysis and design of this type of circuit may be not a simple task. Usually, the simplified models describing the relations of currents and voltages averaged over the switching period are used, in particular their small-signal approximations [1-3]. Such a description contains several small-signal transmittances in s-domain. The step-down (or the Buck converter) is the most popular type of converter and its output characteristics are the object of considerations in this paper.

Fig. 1. The general structure of pulse power converter. PS – power stage, CC – control circuit

The specific applications of Buck converters and the importance of their output characteristics are reviewed in Sec. 2.

The descriptions of the output impedance of Buck converter presented in the literature are briefly presented in Sec. 3. Section 4 is devoted to the alternative way of the description of the output characteristics of the Buck converter. The  $H_r$  transmittance, describing the influence of the changes of the load conductance on the output voltage is considered both for the ideal converter and for converter with parasitic resistances included. The analytical formulas for  $H_r$  as well as the measurements and simulation results are presented.

# 2. Specific requirements for output characteristics of power converters

Output characteristics of power converters are especially important if the converter deliver the electric power to lowvoltage, high-current load, with large values of output current slew rate. The most representative example of such a load is a processor in modern computer equipment. Actually, the supply voltage of such processors are about or below 1.0 V, the current is typically over 100 A, with the slew rate approaching 300 A/ $\mu$ s [4, 5]. For the numbers given above, the equivalent load resistance is below 10 m $\Omega$  and the output resistance of converter should be substantially lower, to ensure a good efficiency. The output voltage of a converter has to be held within narrow limits with the possibility of tight regulation. Converters used to supply the large IC's in modern computers are known as Voltage Regulator Modules (VRM). The step-down (Buck) converters are nearly exclusively used as VRM's in modern processor supply. The main task of VRM is to ensure the Adaptive Voltage Positioning (AVP) for processor. The idea of AVP is to maintain the supply voltage within the specified range in such a way, that for full load, the voltage is slightly below and for no load – slightly above the nominal level [6–8]. It may be accomplished by proper design, resulting in obtaining a constant and sufficient-

<sup>\*</sup>e-mail: wjanke@man.koszalin.pl

W. Janke, M. Baczek, and M. Walczak

ly low closed-loop output impedance over a wide frequency range [7–9]. The closed-loop output impedance  $Z_{cl}$  of converter, i.e. the output impedance of converter with feedback, may be expressed as:

$$Z_{cl} = \frac{Z_{out}}{1 + K_l},\tag{1}$$

where  $Z_{out}$  denote open-loop output impedance of a power stage and  $K_l$  is the loop gain [1, 6, 10]. In fact, the description is more involved, because in the typically used converters with current mode control (CMC), one may observe two independent feedback loops [7, 8, 10]. Other examples of electronic circuits, which demand the stable values of supply voltage, in spite of large and rapid changes of supply current, are some circuits in communication systems, such as pulse operated output power amplifiers in GSM or radar system [11, 12].

There are many efforts presented in the literature, to achieve the satisfactory output impedance of pulse power converters, especially BUCK type. The first, typical way is the sophisticated design of control loops in converters [6–9, 13]. The second way is based on modifications of the basic structure of the power stage [5]. The amount of the literature on the subject is extensive and the references listed above may serve only as examples. The starting point for shaping the output impedance by the proper design of control loop is the precise description of the power stage of converter, in particular – the use of accurate formulas for open-loop output impedance  $Z_{out}$ .

# 3. Open-loop output impedance of Buck converter

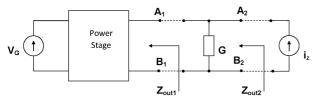

The open-loop output impedance of pulse-modulated power converter (similarly as other transmittances) may be derived by the procedure of averaging and linearization [1–3]. The dependencies for averaged currents and voltages in converter are valid for low frequency range (below one-half of switching frequency). The linearization leads to small-signal dependencies. The output impedance is defined as the output voltage response of converter (Fig. 2) for the excitation of current  $i_Z$  at constant input voltage  $v_G$  and duty ratio  $d_A$ . In some descriptions, the output impedance includes the load conductance G, in other – it does not [6–8, 10, 14–17] – see Fig. 2.

Fig. 2. Two variants of the output impedance of converter

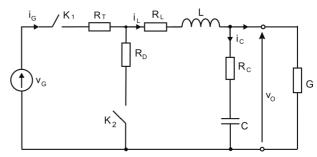

The output impedance may be calculated for the power stage of the Buck converter depicted in Fig. 3, where  $K_1$  and  $K_2$  are switches – main (transistor) and auxiliary (diode or a second transistor), assumed to be ideal.  $R_L$ ,  $R_C$ ,  $R_T$  and  $R_D$  are parasitic resistances of inductor, capacitor and both switches.

Fig. 3. Power stage of Buck converter with parasitic resistances

In many references (for example [10, 16, 17] and even in the widely known textbook of Erickson and Maksimowic [1]) the output impedance of converters is calculated for the ideal case only, i.e. for the assumption  $R_L = R_C = R_T = R_D = 0$ . In such an ideal case, the small-signal averaged equations for the Buck converter in s-domain are:

$$s \cdot L \cdot I_l(s) = D_A \cdot V_g(s) + V_G \cdot \theta(s) - V_o(s), \qquad (2)$$

$$s \cdot C \cdot V_o(s) = -G \cdot V_o(s) + I_l(s). \tag{3}$$

The symbols with capital letter subscripts are quiescent point values; symbols with small letter subscripts – the small-signal values.  $\Theta$  is s-domain representation of small-signal term of duty ratio. Setting  $V_g=0,\ \theta=0,$  i.e. assuming constant input voltage and duty ratio, and assuming the small-signal representation  $I_z$  of current  $i_Z$ , the ideal, open-loop output impedance is easily obtained [1, 14]:

$$Z_{out} = \frac{V_o}{I_z} \Big|_{\substack{V_g = 0 \\ \theta = 0}} = \frac{sL}{s^2LC + sLG + 1}.$$

(4)

The calculations of output impedance for converter with parasitic resistances taken into account, is more involved. In general, the way of including parasitic resistances in deriving averaged, small-signal characteristics of pulse power converters is not obvious and some difficulties or informalities may be observed in the literature, as discussed in [3]. As it is mentioned above, only the ideal case output impedance, similarly as other transmittances of basic converers (with parasitic resistances neglected) are presented in some sources. In the known textbook of Kazimierczuk [2] no analytical formulas for small-signal transmittances of Buck converter are given (although one may derive such formulas from the equivalent circuits). In some papers devoted to discussion of the output impedance of the Buck converter, only the parasitics of capacitor and inductor are included and parasitic resistances of semiconductor switches are neglected without comments [7, 8, 18]. In papers [6] and [13] the following formula for output impedance of Buck converter is given:

$$Z_{out} = R_E \cdot \frac{(1 + s \cdot \omega_C) \cdot (1 + s \cdot \omega_L)}{1 + s/Q \cdot \omega_O) + s^2/\omega_O^2}.$$

(5)

In [13] the quantuity  $R_E$  is not explained and in [6] the comment is given that it includes the resistances of inductor and semiconductor switches, but no respective formula is presented

The above remarks may be concluded, that the problem of analytical description of the output impedance of the Buck

752 Bull. Pol. Ac.: Tech. 60(4) 2012

Output characteristics of step-down (Buck) power converter

converter with parasitics is not solved in the uniform and satisfactory way in the literature. On the other hand, it is observed [19], that parasitic resistances strongly influence the dynamic behavior of pulse power converters, therefore, the design based on simplified formulas for ideal converters or including only a part of parasitics may lead to unsatisfactory results. The averaged, small-signal features of the Buck converter with parasitic resistances may be described by equations obtained with the separation of variables approach, presented in [20].

# 4. Alternative approach to description of output characteristics

There may be some objections to the concept of the output impedance of a power converter. The output characteristics should describe the effect of changes of the load of a converter. The current  $i_Z$  of an independent source in the description of  $Z_{out}$  in the previous Section (see Fig. 2), seems to be not justified physically. In the proposed approach, the load conductance is taken as an additional variable [21]. Instead of the constant load conductance G, the variable conductance  $g_T$  is assumed consisting of "steady state" value and perturbation term:

$$g_T = G + g_t(t). (6)$$

Transmittance  $H_r$  describing the dependence of the output voltage of converter  $v_O$  on the load conductance is derived below for the ideal Buck converter  $(R_T = R_D = R_L = R_C = 0)$ . In such a case, the instantaneous value of inductor current (see Fig. 3) is:

$$i_L = g_T \cdot v_O + C \frac{dv_O}{dt}. \tag{7}$$

Using Eqs. (6) and (7), one obtains following expressions for small-signal term of inductor current (instead of Eq. (3)):

$$I_l = G \cdot V_o + V_O \cdot \Gamma + s \cdot C \cdot V_o, \tag{8}$$

where  $\Gamma$  is the s-domain representation of  $g_t(t)$ . From (2) and (7) it is obtained:

$$V_o = H_a \cdot V_a + H_d \cdot \theta + H_r \cdot \Gamma. \tag{9}$$

Symbols  $H_g$  and  $H_d$  denote the known small-signal transmittances input-to-output and control-to-output [1–3].

$H_r$  transmittance, defined as:

$$H_r = \frac{V_o}{\Gamma} \Big|_{\substack{V_g = 0 \\ \theta = 0}} \tag{10}$$

is, for ideal Buck converter, described by expression:

$$H_r = \frac{-sL \cdot V_O}{s^2LC + sL \cdot G + 1}.$$

(10a)

The derivation of  $H_r$  transmittance in the presence of parasitics is a little more involved. The result is:

$$H_{rp} = \frac{-V_O \cdot [s^2 \cdot L \cdot C \cdot R_C + s \cdot (L + C \cdot R_C \cdot R_Z) + R_Z]}{s^2 L C_Z + s (L \cdot G + C \cdot R_C + C_Z \cdot R_Z) + R_Z \cdot G + 1}, \quad (11)$$

where

$$R_Z = D_A \cdot (R_T - R_D) + R_D + R_L, \tag{12}$$

$$C_Z = C \cdot (1 + R_C \cdot G). \tag{13}$$

The additional subscript "p" means: "with parasitic resistances".

## 5. Results of simulations and measurements

The main purpose of simulations and measurements presented below is to show the quantitative examples of the output characteristics of the Buck converter in frequency- and time-domain; in particular, to demonstrate the influence of parasitic resistances on these characteristics. The parameters of the laboratory model of a converter, including parasitic resistances, are given below. Quiescent point values:  $V_G=12~\rm V;~D_A=0.5;~G=67~\rm mS.$  Switching frequency  $f_s=100~\rm kHz;$  nominal inductance  $100~\rm \mu H;$  capacitance  $470~\rm \mu F;$  measured parasitic resistances of switches:  $R_T=187~\rm m\Omega;~R_D=50~\rm m\Omega.$  Parameters measured at  $1~\rm kHz;~C=419.5~\rm \mu F,~L=96~\rm \mu H,~R_L=67.8~m\Omega;~R_C=121.5~\rm m\Omega.$

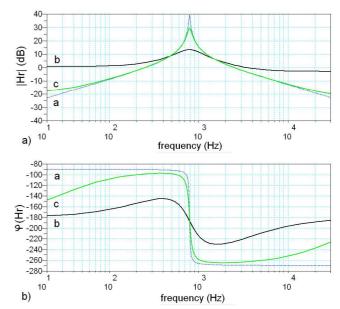

The calculated values of magnitude and phase of  $H_r$  transmittance are presented in Fig. 4 for an ideal case, with parasitics values corresponding to measurements and for parasitics ten times smaller. The substantial differences between the ideal and real case curves are observed. Even by assuming the unnatural values of parasitics (ten times smaller than measured) one obtains the characteristics different from ideal.

Fig. 4. Magnitude (a) and phase (b) of  $H_r$  transmittance calculated from Eq. (12): 1 – ideal case, 2 – with parasitics obtained by measurements, 3 – with parasitics ten times smaller

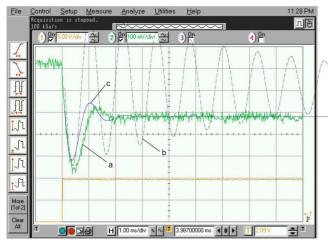

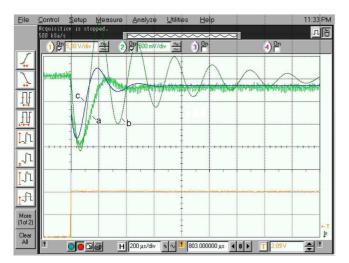

The comparison of the measurements and calculations of time-domain response of output voltage for a step change of load conductance is presented in Fig. 5 obtained for parameter values listed above. Additional measurements and calculations have been performed for capacitance value of 22  $\mu$ F (other parameters the same as above) and results are shown in Fig. 6. Curves (a) are measured, (b) – calculated for ideal converters, (c) – calculated for values of parasitic resistances obtained by independent measurements. The calculated

#### W. Janke, M. Baczek, and M. Walczak

time-domain response corresponds to  $H_r(s)$  transmittance described by Eq. (12). It is observed that measured curves differ substantially from calculation results for an ideal converter and agree reasonably with calculations taking the parasitic resistances into account.

Fig. 5. Output voltage response in time domain for step change of load conductance for  $C=470~\mu\mathrm{F};~\mathrm{a})$  – measurements, b), c) – calculations for ideal case and with parasitic resistances included, respectively

Fig. 6. Output voltage response in time domain for step change of load conductance for  $C=22~\mu\mathrm{F};~a)$  – measurements, b), c) – calculations for ideal case and with parasitic resistances included, respectively

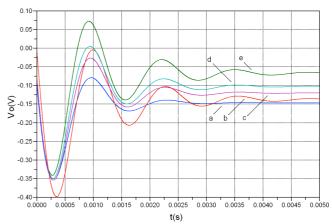

The influence of parasitic resistances on the output voltage transients for a step change of the load conductance for the Buck converter has been observed by additional simulations for the nominal values of parameters listed above and with various combinations of parasitic resistances. The curve (a) in Fig. 7 corresponds to measured values of these resistances. Each of curves (b–e) corresponds to ten times smaller value of a single resistance (curve (b) –  $R_C$ , (c) –  $R_D$ , (d) –  $R_T$  and (e) –  $R_L$ ) with other resistances unchanged. It is observed, that the reduction of  $R_L$  gives the largest effect and reduction of  $R_C$  – the smallest.

Fig. 7. Output voltage response to step change of the load conductance calculated for various combinations of parasitic resistances.

Description in the text

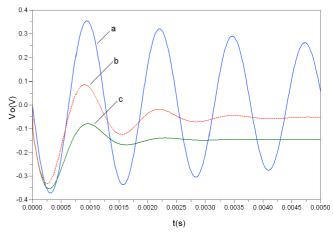

As mentioned in Sec. 3, the parasitic resistances of semiconductor switches are neglected in description of output characteristics of Buck converter in some references (namely [7, 8, 18]). Figure 8 presents the results of simulation experiment showing the consequences of such simplification. The output voltage transients calculated for ideal converter are represented by curve (a); for converter including only parasitics of inductor and capacitor – by curve (b) and for a converter with all parasitic resistances – by curve (c). Neglecting the parasitic resistances of semiconductor switches results in a substantial error in calculations of the output voltage response to step change of the load conductance.

Fig. 8. Output voltage response to step change of the load conductance calculated for ideal converter (a), with parasitics of capacitor and inductor only (b) and for all parasitics included (c)

### 6. Conclusions

Output characteristics of pulse-modulated DC-DC Buck converter have been investigated. The importance of the output characteristics of the Buck converter, especially in application to VRM's used for supplying processors in modern computer equipment is pointed out. It is shown, that in many sources, the influence of parasitic resistances of converter elements on the output impedance of the Buck converter is not described

754 Bull. Pol. Ac.: Tech. 60(4) 2012

#### Output characteristics of step-down (Buck) power converter

properly. One of the main results of the paper is the description of the output characteristics of a converter in the form of  $H_r$  transmittance i.e. an output voltage response to the changes of load conductance. The original formula for  $H_r$  including the influence of parasitic resistances is presented and the examples of calculations of  $H_r$  in frequency domain and corresponding time-domain dependencies are given.

The second important result is the presentation of the strong influence of parasitic resistances of inductor, capacitor and semiconductor switches on the output characteristics of Buck converter. The measurement results differ substantially from calculations for ideal converter (without parasitic resistances) or calculations which take into account only part of parasitic resistances, and are in good accordance with calculations including all these resistances. The results of the reported investigations may be, to the author's believe, useful for design of Buck converters with the shaping of output characteristics by proper control loops.

### REFERENCES

- [1] R.W. Erickson and D. Maksimovic, *Fundamentals of Power Electronics*, 2-nd Ed., Kluwer, Berlin, 2002.

- [2] M.K. Kazimierczuk, *Pulse-Width Modulated DC DC Power Converters*, J. Wiley, London, 2008.

- [3] W. Janke, "Averaged models of pulse-modulated DC-DC converters. Part I. Discussion of standard methods", *Archives of Electrical Engineering* 61 (4), 609–632 (2012).

- [4] Voltage Regulator Module (VRM) and Enterprise Voltage Regulator-Down (EVRD), 11.1 Design Guidelines, Intel Corp., 2009.

- [5] R.P. Singh and A.M. Khambadkone, "A Buck-derived topology with improved step-down transient response", *IEEE Trans. on Power Electronics* 23 (6), 2855–2866 (2008).

- [6] K. Yao, M. Xu, Y. Meng, and F.C. Lee, "Design considerations for VRM transient response based on the output imedance", *IEEE Trans. on Power Electronics* 18 (6), 1270–1277 (2003).

- [7] D. Chen, F.C. Lee, and S.J. Chen, "Evaluation of various Adaptive Voltage Positioning (AVP) schemes for computer power sources", J. Chinese Institution of Engineers 30 (7), 1137–1143 (2007).

- [8] M. Lee, D.C. Huang, K. Chih-Wen, and L. Ben Tai, "Modeling and design for a novel adaptive voltage positioning (AVP)

- scheme for multiphase VRM", *IEEE Trans. on Power Electronics* 23 (4), 1733–1742 (2008).

- [9] S. Xiao, W. Qiu, G. Miller, T.X. Wu, and I. Batarseh, "Adaptive modulation control for multiple-phase voltage regulators", IEEE Trans. on Power Electronics 23 (1), 495–499 (2008).

- [10] R. Ahmadi, D. Paschedag, and M. Ferdowsi, "Closed loop input and output impedances of DC-DC switching converters operating in voltage and current mode control", *IECON 36-th Annual Conf. IEEE Industrial Electronic Society* 1, 2311–2316 (2010).

- [11] C.W. Liu, "Load transient response of a DC/DC converter in GSM/Edge handset applications", *High Frequency Electronics* 1, 18–26 (2007).

- [12] W. Wojtasiak, "The electrothermal modeling of high power microwave FET and its applications", *Electronic and Telecom. Quarterly* 51, 85–104 (2005).

- [13] J.A. Qahouq and V.P. Arikatla, "Power converter with digital sensorless adaptive voltage positioning control scheme", *IEEE Trans. on Industrial Electronics* 58 (9), 4105–4116 (2011).

- [14] "Line and load transient testing for power supplies", Maxim Appl. Note 3443.

- [15] J. Williams, "Load transient response testing for voltage regulators", *Linear Technology Appl. Note* 104, CD-ROM (2006).

- [16] J.T. Mossoba and P.T. Krein, "Output impedance of high performance current mode DC-DC Buck converters, with application to voltage-regulator module control combinations", APEC'04 19-th Annual IEEE Conf. 2, 1315–1321 (2004).

- [17] V. Švikovič, J. A. Oliver, P. Alou, O. Garcia, and J.A. Co-bos, "Synchronous Buck converter with output impedance correction circuit", APEC 2012, 27-th Annual Conf. 1, 727–734 (2012).

- [18] S.K. Mishra, "Design-oriented analysis of modern active droop-controlled power supplies", *IEEE Trans. on Industrial Electronics* 56 (9), 3704–3708 (2009).

- [19] W. Janke, M. Walczak, and M. Bączek, "Input and output characteristics of Buck and Boost converters including parasitic resistances", *Electrical Review* 11 B, 2012, to be published, (in Polish).

- [20] W. Janke, "Averaged models of pulse-modulated DC-DC converters. Part II. Models based on the separation of variables", Archives of Electrical Engineering 61 (4), 633–654 (2012).

- [21] W. Janke, "The extension of small signal model of switching dc-dc power converters", XII Symp. PPEEm'2007 2, 241–246 (2007).

Bull. Pol. Ac.: Tech. 60(4) 2012